技术讲堂:门电路基础

2020-3-13新闻

TTL门电路简介:TTL电路采用双极型工艺制造,具有高速度和品种多等特点。从六十年代开发成功第一代产品以来现有以下几代产品。第一代TTL包括SN54/74系列,(其中54系列工作温度为-55℃~+125℃,74系列工作温度为0℃~+75℃),低功耗系列简称lttl,高速系列简称HTTL。第二代TTL包括肖特基箝位系列(STTL)和低功耗肖特基系列(LSTTL)。第三代为采用等平面工艺制造的先进的STTL(ASTTL)和先进的低功耗STTL(ALSTTL)。由于LSTTL和ALSTTL的电路延时功耗积较小,STTL和ASTTL速度很快,因此获得了广泛的应用。

TTL反相器的基本原理

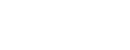

带电阻负载的BJT反相器,其动态性能不理想。在保持逻辑功能不变的前提下,可以另外增加若干元器以改善其动态性能,如减少由于BJT基区电荷存储效应和负载电容所引起的时延。这需改变反相器输入电路和输出电路的结构,以形成TTL反相器的基本电路。下图就是一个TTL反相器的基本电路。

该电路由三部分组成:

由三极管T1组成电路的输入级;

由T3、T4和二极管D组成输出级;

由T2组成的中间级作为输出级的驱动电路,将T2的单端输入信号vI2转换为互补的双端输出信号vI3和vI4,以驱动T3 和T4。

TTL反相器的工作原理

(1)当输入为高电平,如vI=3.6V时,电源VCC通过Rbl和T1的集电结向T2、T3提供基极电流,使T2、T3饱和,输出为低电平,如 vO=0.2V。此时 VB1=VBC1+VBE2+VBE3=(0.7+0.7+0.7)V=2.1V

T1的发射结处于反向偏置,而集电结处于正向偏置。所以T1处于发射结和集电结倒置使用的放大状态。由于T2和T3饱和,输出 VC3 =0.2V,同时可估算出VC2的值:VC2=VCE2+VB3=(0.2+0.7)V=0.9V

此时,VB4=VC2=0.9V。作用于T4的发射结和二极管D的串联支路的电压为VC2-Vo=(0.9-0.2)V=0.7V,显然,T4和D均截止,实现了反相器的逻辑关系:输入为高电平时,输出为低电平。

(2)当输入为低电平且电压为0.2V时,T1的发射结导通,其基极电压等于输入低电压加上发射结正向压降,即:VB1=(0.2+0.7)V=0.9V

此时VB1作用于T1的集电结和T2、T3的发射结上,所以T2、T3都截止,输出为高电平。

由于T2截止,VCC通过RC2向T4提供基极电流,致使T4和D导通,其电流流入负载。

输出电压为vO=Vcc-VBE4-VD=(5-0.7-0.7)V=3.6V

同样也实现了反相器的逻辑关系:输入为低电平时,输出为高电平。

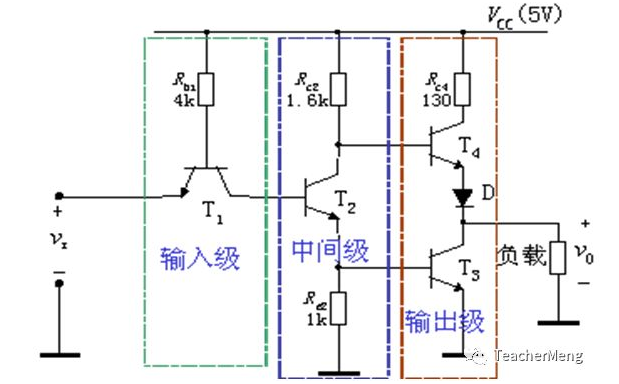

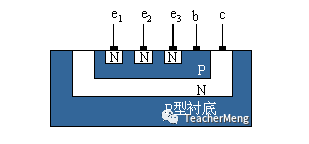

TTL与非门电路

基本TTL反相器不难改变成为多输入端的与非门。它的主要特点是在电路的输入端采用了多发射极的BJT ,如下图所示。器件中的每一个发射极能各自独立地形成正向偏置的发射结,并可促使BJT进人放大或饱和区。两个或多个发射极可以并联地构成一大面积的组合发射极。

下图是采用多发射极BJT用作3输入端TTL与非门的输入器件的一个实例。当任一输入端为低电平时,T1的发射结将正向偏置而导通,T2将截止。结果将导致输出为高电平。只有当全部输入端为高电平时,T1将转入倒置放大状态,T2和T3均饱和,输出为低电平。

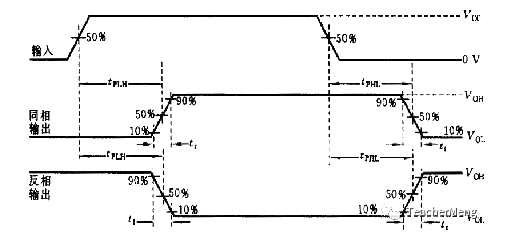

传输延迟时间

这是一个表征门电路开关速度的参数,意味着门电路在输入脉冲波形的作用下,其输出波形相对于输入波形延迟了多长时间。

假设在门电路的输入端加入一脉冲波形、其幅度为0~VCC(单位为V)。相应的的输出波形如下图所示。通常门电路输出由低电平转换高电平或者由高电平转换到低电平所经历的时间分别用tPLH和tPHL表示,有时也采用平均传输延迟时间这一参数,即tPd=(tPLH+tPHL)/2。

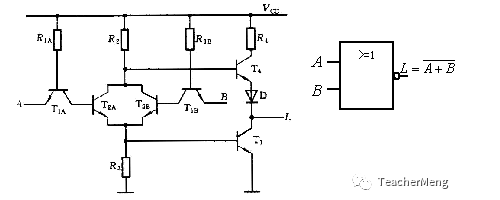

TTL或非门

下图为TTL或非门的逻辑电路及其代表符号。

由图可见,或非逻辑功能是对TTL与非门的结构改进而来,即用两个三极管T2A和T2B代替T2。

若两输入端为低电平,则T2A和T2B均将截止,iB3=0,输出为高电平。

若A、B两输入端中有一个为高电平,则T2A或T2B将饱和,导致iB3>0,iB3便使T3饱和,输出为低电平。这就实现了或非功能。

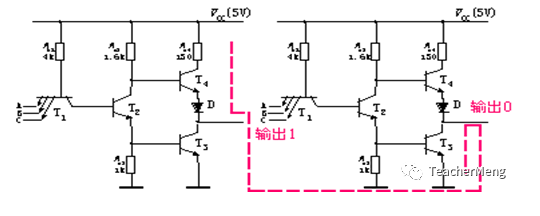

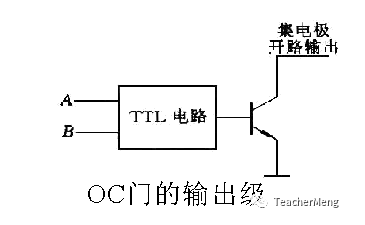

集电极开路门

在工程实践中将两个门的输出端并联以实现与逻辑的功能称为线与。

考察下图所示的情况。当将图中所示的两个逻辑门的输出连接在一起,并且当第一个门的输出为高电平(第一个门的T4导通),第二个门的输出为低电平(第二个门的T3导通)时,正如图中红线所示将出现一个大电流通道,很可能导致晶体管的损坏。

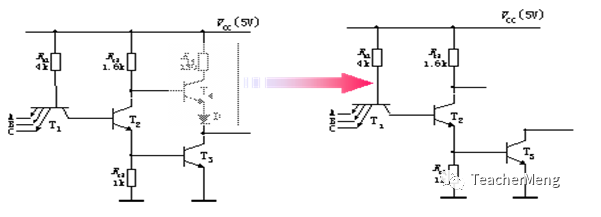

为了避免线与时的产生大电流,可以采用集电极开路门(简称OC门)来解决。所谓集电极开路是指从TTL与非门电路的推挽式输出级中删去电压跟随器,如下图所示:

对于一个两输入端的OC门,其在电路中的符号可用下图来表示:

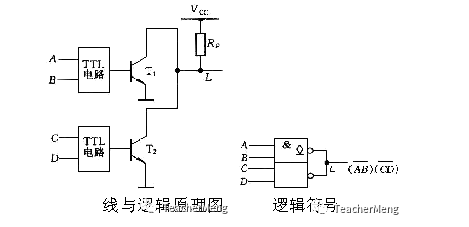

为了实现线与的逻辑功能,可将多个门电路输出管T3的集电极至电源VCC之间,加一公共的上拉电阻RP,如下图所示。为了简明起见,图中以两个OC门并联为例,其中图标“”表示集电极开路之意。

上拉电阻Rp的值可以这样来计算,主要考虑OC门必须驱动一定的拉电流或灌电流负载。有关这两类负载的概念前已讨论,这里仍然适用,所不同的是驱动门是由多个TTL门的输出端直接并联而成。当OC门中的一个TTL门的输出为低电平,其他为高电平时,灌电流将由一个输出BJT(如T1或T2)承担,这是一种极限情况,此时上拉电阻RP具有限制电流的作用。为保证IOL不超过额定值IOL(max),必须合理选用RP的值。例如VCC=5V,RP=1kΩ,则IOL=5mA。

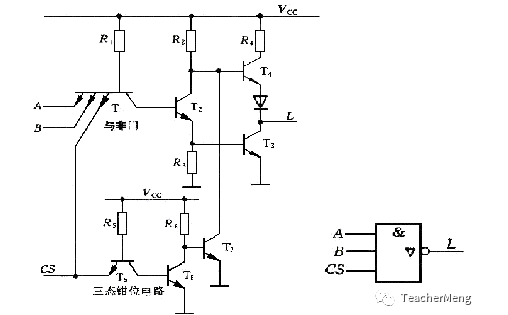

三态与非门(TSL)

利用OC门虽然可以实现线与的功能,但外接电阻Rp的选择要受到一定的限制而不能取得太小,因此影响了工作速度。同时它省去了有源负载,使得带负载能力下降。为保持推拉式输出级的优点,还能作线与联接,人们又开发了一种三态与非门,它的输出除了具有一般与非门的两种状态,即输出电阻较小的高、低电平状态外,还具有高输出电阻的第三状态,称为高阻态,又称为禁止态。

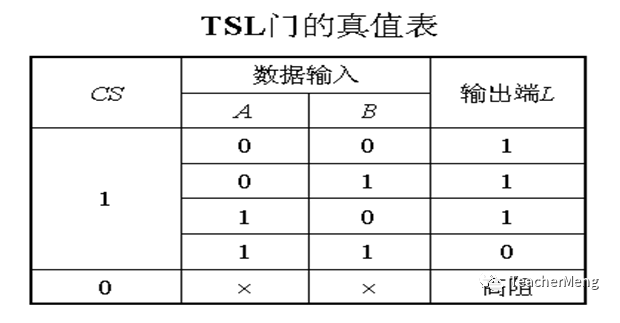

一个简单的TSL门的电路如上图所示。其中CS为片选信号输入端,A、B为数据输入端。

当CS=1时,TSL门电路中的T5处于倒置放大状态,T6饱和,T7截止,即其集电极相当于开路。此时输出状态将完全取决于数据输入端A、B的状态,电路输出与输入的逻辑关系与一般与非门相同。这种状态称为TSL的工作状态。

当CS=0时T7导通,使T4的基极钳制于低电平。同时由于低电平的信号送到T1的输入端,迫使T2和T3截止。这样T3和T4均截止,门的输出端L出现开路,既不是低电平,又不是高电平,这就是第三工作状态。这样,当CS为高电平时,TSL门的输出信号送到总线,而当CS为低电平时,门的输出与数据总线断开,此时数据总线的状态由其他门电路的输出所决定。

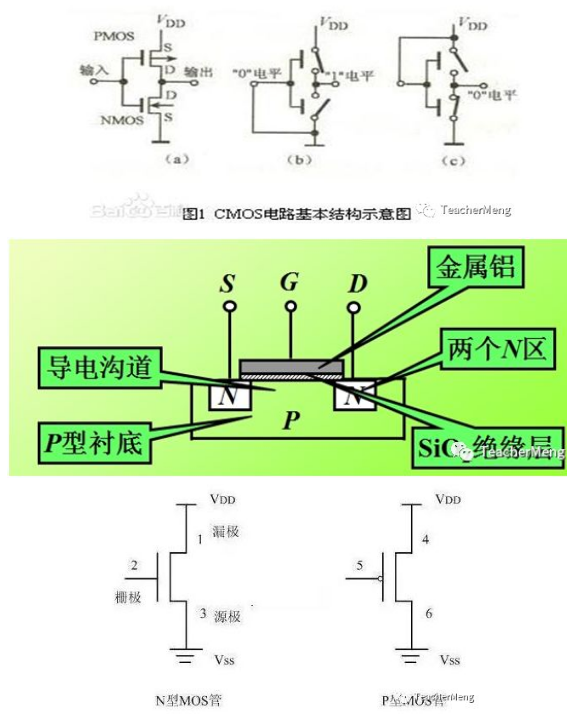

CMOS门电路简介:CMOS电路是互补型金属氧化物半导体电路(Complementary Metal-Oxide-Semiconductor)的英文字头缩写,它由绝缘场效应晶体管组成,由于只有一种载流子,因而是一种单极型晶体管集成电路,其基本结构是一个N沟道MOS管和一个P沟道MOS管。

CMOS工作原理:由于两管栅极工作电压极性相反,故将两管栅极相连作为输入端,两个漏极相连作为输出端,如图1(a)所示,则两管正好互为负载,处于互补工作状态。当输入低电平(Vi=Vss)时,PMOS管导通,NMOS管截止,输出高电平,如图1(b)所示。 ·当输入高电平(Vi=VDD)时,PMOS管截止,NMOS管导通,输出为低电平,如图1(c)所示。两管如单刀双掷开关一样交替工作,构成反相器。

CMOS逻辑电平

高速CMOS电路的电源电压VDD通常为+5V;Vss接地,是0V。 高电平视为逻辑“1”,电平值的范围为:VDD的65%~VDD(或者VDD-1.5V~VDD)。低电平视作逻辑“0”,要求不超过VDD的35%或0~1.5V。+1.5V~+3.5V应看作不确定电平。在硬件设计中要避免出现不确定电平。

近年来,随着亚微米技术的发展,单片机的电源呈下降趋势。低电源电压有助于降低功耗。VDD为3.3V的CMOS器件已大量使用。在便携式应用中,VDD为2.7V,甚至1.8V的单片机也已经出现。将来电源电压还会继续下降,降到0.9V,但低于VDD的35%的电平视为逻辑“0”,高于VDD的65%的电平视为逻辑“1”的规律仍然是适用的。

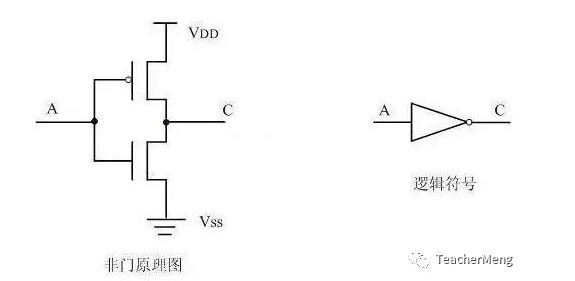

非门

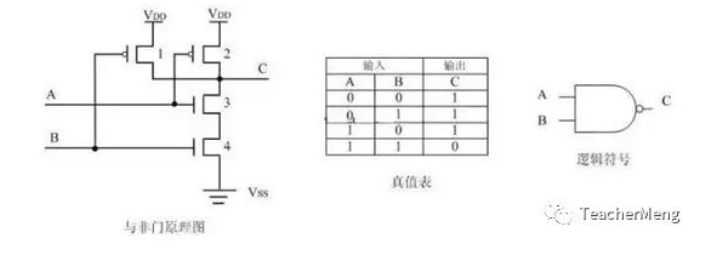

与非门

与非门工作原理:

①、A、B输入均为低电平时,1、2管导通,3、4管截止,C端电压与VDD一致,输出高电平。

②、A输入高电平,B输入低电平时,1、3管导通,2、4管截止,C端电位与1管的漏极保持一致,输出高电平。

③、A输入低电平,B输入高电平时,情况与②类似,亦输出高电平。

④、A、B输入均为高电平时,1、2管截止,3、4管导通,C端电压与地一致,输出低电平。

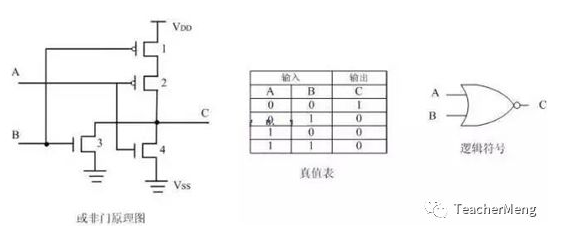

或非门

或非门工作原理:

①、A、B输入均为低电平时,1、2管导通,3、4管截止,C端电压与VDD一致,输出高电平。

②、A输入高电平,B输入低电平时,1、4管导通,2、3管截止,C端输出低电平。

③、A输入低电平,B输入高电平时,情况与②类似,亦输出低电平。

④、A、B输入均为高电平时,1、2管截止,3、4管导通,C端电压与地一致,输出低电平。

注:将上述“与非”门、“或非”门逻辑符号的输出端的小圆圈去掉,就成了“与”门、“或”门的逻辑符号。而实现“与”、“或”功能的电路图则必须在输出端加上一个反向器,即加上一对CMOS管,因此,“与”门实际上比“与非”门复杂,延迟时间也长些,这一点在电路设计中要注意。

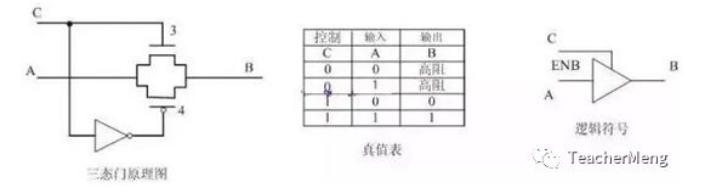

三态门

三态门的工作原理:

当控制端C为“1”时,N型管3导通,同时,C端电平通过反向器后成为低电平,使P型管4导通,输入端A的电平状况可以通过3、4管到达输出端B。

当控制端C为“0”时,3、4管都截止,输入端A的电平状况无法到达输出端B,输出端B呈现高电阻的状态,称为“高阻态”。

这个器件也称作“带控制端的传输门”。带有一定驱动能力的三态门也称作“缓冲器”,逻辑符号是一样的。

注:从CMOS等效电路或者真值表、逻辑表达式上都可以看出,把“0”和“1”换个位置,“与非”门就变成了“或非”门。对于“1”有效的信号是“与非”关系,对于“0”有效的信号是“或非”关系。

上述图中画的逻辑器件符号均是正逻辑下的输入、输出关系,即对“1”(高电平)有效而言。而单片机中的多数控制信号是按照负有效(低电平有效)定义的。例如片选信号CS(ChipSelect),指该信号为“0”时具有字符标明的意义,即该信号为“0”表示该芯片被选中。因此,“或非”门的逻辑符号也可以画成下图。